Миниатюрная измерительная система-на-кристалле SD6500

15 августа 2024

Сергей и Алексей Поповы (г. Воронеж)

Система-на-кристалле класса «analog-front-end» SD6500 производства китайской компании SDIC Microelectronics – идеальная по соотношению «цена-качество» основа для создания портативного лабораторного или переносного измерительного прибора, прежде всего – с батарейным питанием.

Основанная в 2005 году компания SDIC Microelectronics (КНР) производит разнообразные аналоговые и аналого-цифровые микросхемы с высоким уровнем интеграции. В настоящее время производственный портфель компании включает:

- микросхемы для промышленного оборудования, в том числе микросхемы HART-модемов, являющиеся аналогами соответствующей продукции ведущих мировых производителей; микросхемы ЦАП токовой петли (4…20) мА (16 бит, интегральная нелинейность не более 0,01%);

- микросхемы для измерительных систем и приборов с высоким уровнем интеграции (системы-на-кристалле), предназначенные в первую очередь для инфракрасных термометров и пирометров, весов, датчиков давления в шинах, с поддержкой различных типов дисплеев, с интеграцией 32-битных микроконтроллерных ядер и памяти, а также сверхмикропотребляющие;

- микросхемы для построения цифровых мультиметров средней точности (шкалы 33/4…41/2 разряда) широкого применения;

- микросхемы датчиков температуры повышенной точности с цифровыми интерфейсами (не требующие калибровки у пользователя), являющиеся аналогами соответствующей продукции ведущих мировых производителей.

Объем продаж SDIC Microelectronics составляет свыше 100 миллионов микросхем в год.

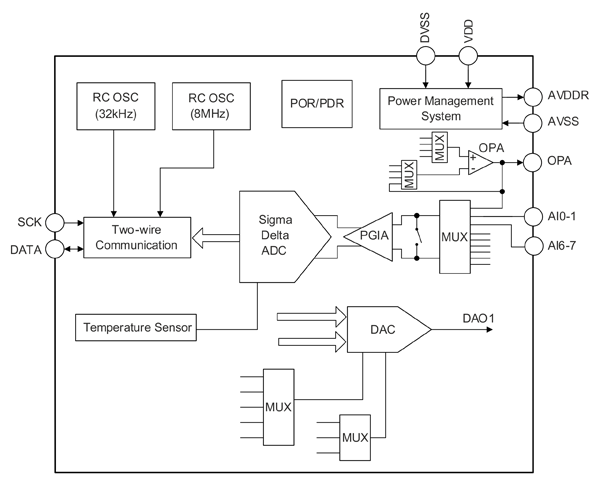

Рассмотрим подробнее систему-на-кристалле класса «analog-front-end» SD6500, на основе которой можно создавать различные высокоточные, миниатюрные, микропотребляющие, при этом – недорогие измерительные и управляющие приборы и системы. Функциональная схема SD6500 показана на рисунке 1.

Рис. 1. Функциональная схема SD6500

В корпусе MSOP10 интегрированы: 24-битный сигма-дельта АЦП с малошумящим предусилителем и широкими возможностями выбора источников входных сигналов, режимов работы, скорости и коэффициентов усиления; 8-битный ЦАП с развитой системой мультиплексирования по входу и выходу; мультиплексируемый многоцелевой операционный усилитель; подсистема питания (настраиваемый LDO-стабилизатор напряжения питания аналоговых блоков ИМС и аналоговых внешних цепей, а также буферизированный источник опорного напряжения); подсистема мультиплексирования функционала внешних выводов микросхемы; два тактовых RC-генератора – 8 МГц и 32 кГц; универсальный двухпроводной интерфейс для связи с хост-контроллером; контроллер переключения между активным режимом и режимом микропотребления; термодатчик; детектор недопустимого понижения напряжения питания (ниже 1,9 В) и схема инициализации при подаче или восстановлении должного напряжения питания (2,4…3,6) В. И все это богатство возможностей – при потреблении 1,6 мА в активном режиме и 1 мкА в спящем. Рабочие режимы, функционал и параметры преобразования настраиваются при помощи внутренних регистров микросхемы, которые конфигурируются внешним хост-контроллером через двухпроводный последовательный интерфейс.

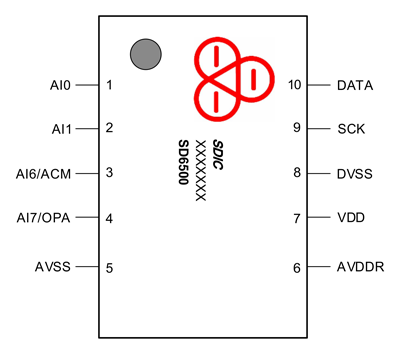

На рисунке 2 показано функциональное назначение внешних выводов SD6500 в корпусе MSOP10; в таблице 1 это поясняется более подробно.

Рис. 2. Функциональное назначение внешних выводов SD6500 в корпусе MSOP10

Таблица 1. Назначение и функциональные возможности на внешних выводах SD6500 в корпусе MSOP10

| Номера выводов в корпусе MSOP10 | Наименования выводов | Описание назначения и функциональных возможностей |

|---|---|---|

| 1 | AI0 | Вход аналогового сигнала для АЦП |

| 2 | AI1 | Вход аналогового сигнала для АЦП |

| 3 | AI6/ACM | Вход аналогового сигнала для АЦП или выход буфера ИОН |

| 4 | AI7/OPA | Вход аналогового сигнала для АЦП или выход операционного усилителя |

| 5 | AVSS | Общий (минус) аналоговых цепей |

| 6 | AVDDR | Стабилизированное напряжение питания (плюс) аналоговых цепей |

| 7 | VDD | Внешнее напряжение питания; плюс питания цифрового интерфейса |

| 8 | DVSS | Общий (минус) внешнего питания; минус питания цифрового интерфейса |

| 9 | SCK | Вход для тактового сигнала двухпроводного интерфейса (генерируется хост-контроллером) |

| 10 | DATA | Вход или выход; линия данных двухпроводного интерфейса |

Предельно допустимые значения параметров SD6500 представлены в таблице 2, а основные нормируемые технические характеристики – в таблице 3.

Таблица 2. Предельно допустимые значения параметров SD6500

| Обозначение | Параметр | Минимально допустимо | Максимально допустимо |

|---|---|---|---|

| TA | Диапазон рабочих температур, °С | -40 | 85 |

| TS | Диапазон температур при хранении, °С | -55 | 150 |

| VDD | Напряжение внешнего питания, В | -0,2 | 4 |

| VIN, VOUT | Напряжения на входах и выходах, В | -0,2 | VDD+0,3 |

| TL | Профиль температурного режима пайки | Согласно IPC/JEDECJ-STD-020C | |

Таблица 3. Нормируемые технические характеристики SD6500 (при напряжении внешнего питания 3 В и температуре окружающей среды 25°С)

| Обозначение | Параметр | Минимальное | Типовое | Максимальное | Примечание |

|---|---|---|---|---|---|

| VDD | Напряжение внешнего питания, В | 2,4 | 3,3 | 3,6 | – |

| FOSC | Внутренняя тактовая частота, МГц | – | 8 | – | – |

| IHRC | Частота встроенного ВЧ тактового генератора, МГц | – | 8 | – | – |

| ILRC | Частота встроенного НЧ тактового генератора, кГц | – | 32 | – | – |

| IDD1 | Ток потребления в активном режиме работы, мА | – | 1,6 | – | Все аналоговые блоки активны; без внешних нагрузок |

| IDD2 | Ток потребления в спящем режиме работы, мкА | – | 1 | – | Микросхема в спящем режиме |

| FSAM | Частота выборок АЦП, кГц | – | – | 512 | – |

| OSR | Кратность оверсэмплинга АЦП | 128 | – | 16384 | – |

| NFbit | Динамический диапазон АЦП выше уровня шумовой дорожки от пика до пика, бит | – | 16 | – | При усилении предусилителя =128 и полной шкале по входу ±4мВ |

| NMbit | Разрешение АЦП без пропуска кодов, бит | – | – | 24 | – |

| INL | Интегральная нелинейность АЦП, % полной шкалы | – | 0,002 | – | – |

| VIN DIFF | Рабочие диапазоны входного дифференциального напряжения предусилителя АЦП, в зависимости от его дифференциального коэффициента усиления (VREF= (AVDDR или ACM)*(0,125…1)) | -VREF | – | VREF | При усилении = 1 |

| -VREF/4 | – | VREF/4 | При усилении = 4 | ||

| -VREF/8 | – | VREF/8 | При усилении = 8 | ||

| -VREF/16 | – | VREF/16 | При усилении = 16 | ||

| -VREF/32 | – | VREF/32 | При усилении = 32 | ||

| -VREF/64 | – | VREF/64 | При усилении = 64 | ||

| -VREF/128 | – | VREF/128 | При усилении = 128 | ||

| -VREF/256 | – | VREF/256 | При усилении = 256 | ||

| VIN | Рабочие диапазоны входных напряжений (относительно AVSS) предусилителя АЦП, в зависимости от его режима работы, В | Минус 0,3 | – | AVDDR | При усилении предусилителя = 1 и шунтированном входном буфере АЦП |

| 0,3 | – | AVDDR-0,7 | При усилении предусилителя ≥4, а также при усилении предусилителя = 1 и активированном входном буфере АЦП | ||

| VACM | Напряжение буфера ИОН, В | – | 1,2 | – | – |

| I ACM SOUR | Допустимый вытекающий ток нагрузки буфера ИОН, мА | – | 1 | – | – |

| I ACM SINK | Допустимый втекающий ток нагрузки буфера ИОН, мА | – | 1 | – | – |

| PSR ACM | Изменение напряжения буфера ИОН при вариациях внешнего питания, мВ/В | – | 0,1 | – | – |

| VAVDDR | Стабилизированное напряжение питания аналоговых блоков, В (программируемое) | – | 2,4 | – | Биты AVDDRX[1:0]=00 |

| – | 2,7 | – | Биты AVDDRX[1:0]=01 | ||

| – | 3,0 | – | Биты AVDDRX[1:0]=10 | ||

| – | 3,3 | – | Биты AVDDRX[1:0]=11 | ||

| IAVDDR | Допустимый вытекающий ток нагрузки стабилизатора напряжения AVDDR, мА | – | 10 | – | – |

| POR | Пороговое значение нарастающего напряжения питания микросхемы, при котором происходит ее инициализация, В | – | 2,0 | – | – |

| LVD | Пороговое значение недопустимого понижения напряжения питания микросхемы, В | – | 1,9 | – | – |

| THlbt | Гистерезис детектора недопустимого понижения напряжения питания микросхемы, В | – | 0,2 | – | – |

| Параметры цифрового интерфейса с хост-контроллером | |||||

| VIH | Логическая единица на входе | 0,7×VDD | – | – | – |

| VIL | Логический ноль на входе | – | – | 0,3×VDD | – |

| VOH | Логическая единица на выходе | VDD-0,3 В | – | – | – |

| VOL | Логический ноль на выходе | – | – | VSS+0,3В | – |

Хост-контроллер управляет ИС SD6500, конфигурирует и задает режимы работы аналоговых блоков, а также получает результаты измерений посредством записи и чтения регистров в составе SD6500. Всего имеется 20 регистров ввода-вывода шириной 1 байт. В таблице 4 представлены сводные данные по всем регистрам. Более детально их применение описано далее, при рассмотрении конкретных аналоговых блоков, с которыми они взаимодействуют.

Таблица 4. Регистры ввода-вывода в SD6500

| Адрес регистра | Наименование регистра | Назначение и наименование отдельных бит и групп бит в регистрах | |||||||

|---|---|---|---|---|---|---|---|---|---|

| Бит7 | Бит6 | Бит5 | Бит4 | Бит3 | Бит2 | Бит1 | Бит0 | ||

| 00H | SYSCON | – | – | A6S | WTIME[2:0] | ADIF | SLEEP | ||

| 01H | ASPM | GS[2:0] | PGIAEN | TEN | BUFO | IAD | ADCEN | ||

| 02H | IAOS | – | SI | OSEN | OSSIGN | OS[3:0] | |||

| 03H | ASPMUXS1 | – | – | VREFG[1:0] | VREFS[1:0] | RCS[1:0] | |||

| 04H | ASPMUXS2 | IAINPS[3:0] | IAINNS[3:0] | ||||||

| 05H | DFM | – | DCSET[2:0] | – | OSR[2:0] | ||||

| 06H | ASPCK1 | ASPCK1[7:0] | |||||||

| 07H | ASPCK2 | BUFFDS[1:0] | IAFDS[2:0] | – | – | – | |||

| 08H | ADCDH | ADCD[23:16] | |||||||

| 09H | ADCDM | ADCD[15:8] | |||||||

| 0AH | ADCDL | ADCD[7:0] | |||||||

| 0BH | THRH | THR[15:8] | |||||||

| 0CH | THRM | THR[7:0] | |||||||

| 0DH | ZEROH | ZERO[15:8] | |||||||

| 0EH | ZEROM | ZERO[7:0] | |||||||

| 0FH | COMPCON | – | – | – | EFFECT | UPDATE | CNT[2:0] | ||

| 12H | OPASEL | EN_OPA | OPACS | OPAPS[1:0] | OPANS[1:0] | – | – | ||

| 14H | DASEL | DAEN | DAP[3:0] | DAN[2:0] | |||||

| 15H | DAO1 | DABIT1[7:0] | |||||||

| 17H | AVDDR | – | – | AVDDRX[1:0] | – | – | – | – | |

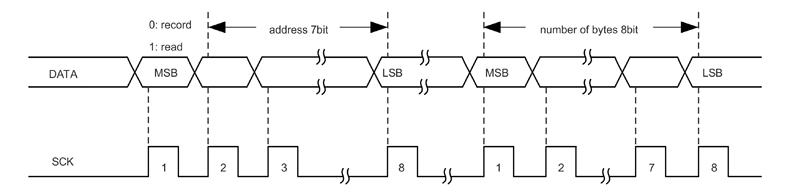

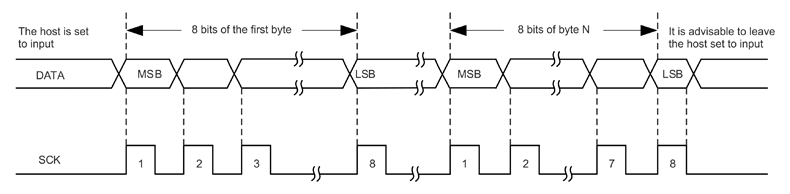

Обмен между хост-контроллером и SD6500 производится по двум линиям: SCK и DATA. Тактовый сигнал частотой до 1,1 МГц генерируется хостом. Линия DATA – двунаправленная. В процессе инициализации ИМС при подаче внешнего питания или его восстановлении после проседания SD6500 устанавливается на чтение. Для гибкости применения линия DATA внутри SD6500 не подтянута резисторами ни к земле, ни к питанию – это должен обеспечить пользователь. Начало обмена инициализируется хостом путем посылки двух командных байт (рисунок 3). Значение старшего бита первого командного байта определяет цель обмена: запись или чтение. Последующие биты первого командного байта определяют адрес регистра ввода-вывода (корректно воспринимаются 64 адреса регистров – 0x00…0x3F; если значение адреса больше 0x3F, то запись в регистры ввода-вывода не происходит, а при чтении хосту возвращаются нули). Как указано в таблице 4, SD6500 имеет 20 регистров с адресами от 0x00 до 0x17. Второй командный байт определяет количество байт последующего обмена (корректно воспринимаются значения N = 1…64), записываемых (рисунок 4) или читаемых (рисунок 5) за один цикл обмена.

Рис. 3. Командные байты, начинающие цикл обмена между хост-контроллером и ИМС SD6500

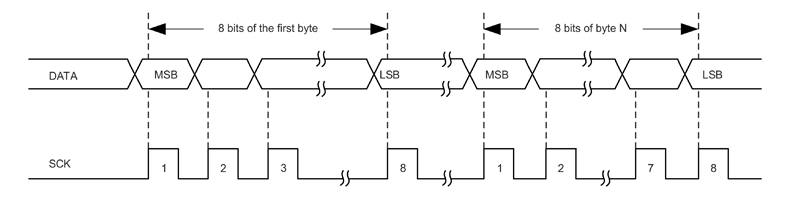

ИМС SD6500 считывает данные, передаваемые хост-контроллером, на спадающем фронте тактового сигнала SCK (рисунок 4)

Рис. 4. Запись N байт хост-контроллером в цикле обмена

ИМС SD6500 устанавливает данные, для их чтения хост-контроллером, на нарастающем фронте тактового сигнала SCK (рисунок 5). В цикле чтения после передачи двух командных байт (рисунок 3) хост освобождает линию DATA.

Рис. 5. Чтение N байт хост-контроллером в цикле обмена

Также на нарастающем фронте тактового сигнала SCK происходит захват и освобождение линии DATA. Кроме того, сигнал SCK внутренне задерживается в SD6500 (по крайней мере, на 60 нс) для удовлетворения требований по времени установления данных для их чтения хост-контроллером. Для исключения коллизий при захвате/освобождении линии DATA, хост должен делать это корректно (данная функция – его обязанность, так как именно он генерирует сигнал SCK). Хост-контроллер должен освобождать линию DATA не позднее начала нарастающего фронта сигнала SCK, а захватывать ее не ранее, чем через 60 нс после нарастающего фронта сигнала SCK – тогда SD6500 способен это понять и корректно отреагировать.

SD6500 поддерживает три режима работы: нормальный, спящий и спящий с самопробуждением. В нормальном (активном) режиме, который устанавливается по умолчанию при инициализации микросхемы, АЦП выполняет регулярные преобразования. Хост-контроллер, читая флаг ADIF (бит 1 в регистре SYSCON), может отслеживать готовность нового результата АЦП. Если ADIF=0, то результат еще не готов. Если ADIF=1, можно прочитать новый результат в регистрах ADCDH:ADCDM:ADCDL. При чтении результата ADIF аппаратно очищается.

Если при работе в нормальном режиме SD6500 обнаруживает, что сигнал SCK, который генерируется хостом, остается высоким в течение, по крайней мере, 12 мс (время измеряется по НЧ генератору 32 кГц), то микросхема автоматически переключается в спящий режим или спящий с самопробуждением – это зависит от настроек: битов SLEEP и WTIME[2:0] в регистре SYSCON. Если SLEEP=0, то беспробудный сон; если SLEEP=1, то регулярное самопробуждение. Возврат из спящих режимов в нормальный происходит при обнаружении SCK=0 (это – условие наивысшего приоритета и единственная возможность пробуждения при SLEEP=0) или по истечении заданного времени сна (в режиме с самопробуждением), которое можно выбрать из восьми вариантов в диапазоне от 0,1 до 3 с, при этом время устанавливается с помощью WTIME[2:0]. При самопробуждении АЦП выполняет, по крайней мере, три преобразования (количество преобразований определяется значением бита EFFECT в регистре COMPCON). В зависимости от его результата (анализируются старшие 16 бит в регистрах ADCDH:ADCDM), в сравнении со значениями предыдущих преобразований (хранятся в регистрах ZEROH:ZEROM) и настройками, хранящимися в регистрах THRH:THRM, COMPCON (биты UPDATE и CNT[2:0]), SD6500 выполняет дальнейшие действия. Если новый результат АЦП незначительно отличается от предыдущих или скорость его изменения во времени не превышает заданных уставок, то продолжается спящий режим с периодическим самопробуждением. Если же достоверно установлено, что появились новые данные АЦП, которые могут представлять интерес для хост-контроллера, то SD6500 на 10 мс переводит линию DATA в низкий уровень, привлекая внимание хоста (например, также пробуждая его от сна). Таким образом, с учетом малой потребляемой мощности в спящих режимах, SD6500 отлично подходит для применения в портативной лабораторной и измерительной технике, а также в устройствах с батарейным питанием.

При нормальном режиме работы микросхемы SD6500 активен ВЧ тактовый генератор частотой 8 МГц±20%. При переключении ИС в спящие режимы ВЧ генератор отключается. Если выбран спящий режим с самопробуждением, работает НЧ тактовый генератор частотой 32 кГц, отсчитывая заданные интервалы времени до пробуждения. НЧ генератору при подаче внешнего питания на SD6500 требуется 32 мс для выхода на установившийся режим.

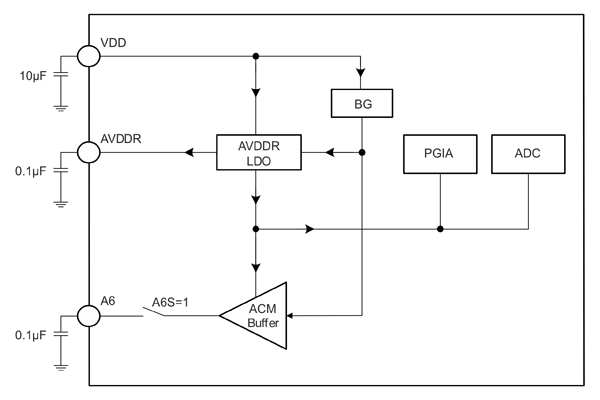

Подсистема питания ИМС SD6500 показана на рисунке 6. Она содержит: линейный стабилизатор с малым падением напряжения, имеющий нагрузочную способность 10 мА и обладающий возможностью программировать значение выходного напряжения AVDDR, а также микромощный термостабильный источник опорного напряжения и его буфер-повторитель с нагрузочной способностью до ±1 мА (напряжение на выходе буфера обозначается как ACM). Стабилизатор AVDDR также использует термостабильный ИОН в качестве опорного напряжения и программируется битами AVDDRX[1:0] в регистре AVDDR (значения напряжений смотреть в таблице 2). При инициализации микросхемы AVDDRX[1:0]=00 и, соответственно, напряжение AVDDR=2,4 В. Стабилизатор AVDDR используется для питания АЦП, его предусилителя, других аналоговых блоков SD6500, а также может питать внешние датчики. Напряжение ACM с выхода буфера может быть использовано в различных цепях внутри микросхемы, а также может быть мультиплексировано на вывод 3 при установлении бита A6S=1 в регистре SYSCON. В этом случае данный вывод микросхемы следует шунтировать внешним конденсатором емкостью 100 нФ. Стабилизатор AVDDR и буфер ACM не имеют собственных, явно выраженных логических сигналов разрешения работы и управляются (включаются и выключаются) в зависимости от выбранного текущего режима работы.

Рис. 6. Подсистема питания ИМС SD6500

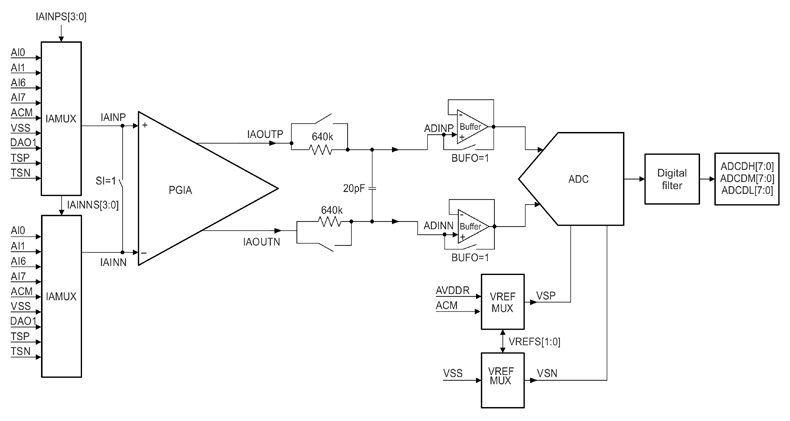

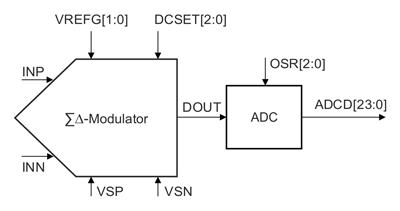

Подсистема обработки аналоговых сигналов ASP показана на рисунке 7. Она включает мультиплексоры входных аналоговых сигналов, предусилитель (малошумящий инструментальный усилитель с программируемым коэффициентом усиления и дифференциальным выходом), аналоговый фильтр и буферы на входах АЦП, 24-битный сигма-дельта АЦП с выбором опорного напряжения и скорости преобразования, выходной цифровой фильтр, регистры хранения последнего результата АЦП.

Рис. 7. Подсистема обработки аналоговых сигналов ASP

Для конфигурации блоков в составе ASP и настроек режимов их работы используются семь регистров: ASPM, ASPMUXS1, ASPMUXS2, IAOS, ASPCK1, ASPCK2, DFM.

Входные мультиплексоры позволяют выбирать в качестве обрабатываемых аналоговых сигналов любые из девяти вариантов: четыре сигнала с внешних выводов микросхемы AI0, AI1, AI6, AI7; опорное напряжение ACM; ноль (общий) AVSS; выход ЦАП DAO1; выводы термодатчика TSP и TSN. Причем весь этот набор сигналов может быть независимо скоммутирован как на неинвертирующий, так и на инвертирующий входы предусилителя. В том числе, на оба входа предусилителя могут быть поданы одинаковые напряжения, а также эти входы можно замкнуть между собой. Это дает гибкие возможности калибровки. Входные мультиплексоры управляются битами IAINPS[3:0] и IAINNS[3:0] в регистре ASPMUXS2 и переключают сигналы на входы предусилителя в соответствии с таблицей 5. Ключ, коммутирующий входы предусилителя на землю или между собой, управляется битом SI в регистре IAOS.

Таблица 5. Мультиплексирование сигналов на входы инструментального усилителя

| биты IAINPS[3:0] | Сигналы на неинвертирующем входе | биты IAINNS[3:0] | Сигналы на инвертирующем входе |

|---|---|---|---|

| 0000 | AI0 | 0000 | AI0 |

| 0001 | AI1 | 0001 | AI1 |

| 0010 | зарезервировано | 0010 | зарезервировано |

| 0011 | зарезервировано | 0011 | зарезервировано |

| 0100 | зарезервировано | 0100 | зарезервировано |

| 0101 | зарезервировано | 0101 | зарезервировано |

| 0110 | AI6 | 0110 | AI6 |

| 0111 | AI7 | 0111 | AI7 |

| 1000 | ACM | 1000 | ACM |

| 1001 | AVSS | 1001 | AVSS |

| 1010 | зарезервировано | 1010 | зарезервировано |

| 1011 | DAO1 | 1011 | DAO1 |

| 1100 | зарезервировано | 1100 | зарезервировано |

| 1101 | зарезервировано | 1101 | зарезервировано |

| 1110 | TSP | 1110 | TSP |

| 1111 | TSN | 1111 | TSN |

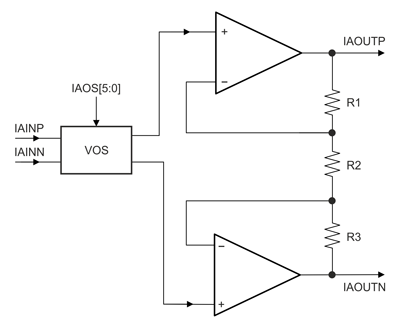

Упрощенная схема инструментального усилителя (предусилителя) показана на рисунке 8. Он имеет дифференциальные входы (IAINP и IAINN) с высоким входным сопротивлением и низкоомные дифференциальные выходы (IAOUTP и IAOUTN). Рекомендуемый рабочий диапазон напряжений на входах предусилителя IAINP и IAINN относительно общего (AVSS) – от 0,7 В до (AVDDR-1 В). Рабочий диапазон напряжений на выходах предусилителя IAOUTP и IAOUTN относительно общего (AVSS) – от 0,3 В до (AVDDR-0,9 В). Инструментальный усилитель усиливает дифференциальный сигнал (IAINP — IAINN) (с добавкой напряжения смещения по входу, складывающегося из специально введенной программируемой компоненты VOS и малого собственного напряжения смещения, то есть ошибки, усилителя). Коэффициент усиления дифференциального сигнала КИУ=Δ(IAOUTP – IAOUTN)/Δ(IAINP – IAINN+ VOS) программируется сопротивлением резистора R2: КИУ=2×R1/R2+1 при фиксированных R1=R3. Синфазное напряжение на входах IAINP и IAINN усилителя передается на выходы IAOUTP и IAOUTN без усиления.

Рис. 8. Упрощенная схема предусилителя

Для наиболее полного использования рабочего диапазона напряжений предусилителя при обработке входных сигналов с существенно несимметричной дифференциальной составляющей, к ним можно добавить постоянное дифференциальное смещение VOS. Напряжение смещения по входу предусилителя VOS программируется битами OS[3:0], OSSIGN и OSEN в регистре IAOS. При сбросе бита OSEN=0 схема задания дифференциального смещения по входу предусилителя VOS выключается и, соответственно, VOS=0. Бит OSSIGN определяет знак дифференциального смещения VOS, а битами OS[3:0] программируют его модуль. Конкретные значения VOS (при OSEN=1) зависят от выбранного стабилизированного напряжения AVDDR и установленного дифференциального коэффициента усиления. В частности, при AVDDR=2,4 В и КИУ=128 или 256, напряжение смещения по входу предусилителя VOS программируется в соответствии с таблицей 6. При других значениях AVDDR модуль VOS изменяется приблизительно пропорционально изменениям AVDDR. При КИУ менее 128 рекомендуется отключать VOS заданием OSEN=0.

Таблица 6. Пример программирования значений модуля напряжения смещения по входу предусилителя VOS при AVDDR=2,4 В и КИУ=128 или 256

| Смещение при КИУ=256 | Смещение при КИУ=128 | ||

|---|---|---|---|

| биты OS[3:0] | VOS (мВ) | биты OS[3:0] | VOS (мВ) |

| 0000 | 1,04 | 0000 | 2,08 |

| 0001 | 2,11 | 0001 | 4,22 |

| 0010 | 3,16 | 0010 | 6,32 |

| 0011 | 4,32 | 0011 | 8,64 |

| 0100 | 5,47 | 0100 | 10,94 |

| 0101 | 6,57 | 0101 | 13,14 |

| 0110 | 7,82 | 0110 | 15,64 |

| 0111 | 9,12 | 0111 | 18,24 |

| 1000 | 10,26 | 1000 | 20,52 |

| 1001 | 11,73 | 1001 | 23,46 |

| 1010 | 12,96 | 1010 | 25,92 |

| 1011 | 14,49 | 1011 | 28,98 |

| 1100 | 15,89 | 1100 | 31,78 |

| 1101 | 17,59 | 1101 | 35,18 |

| 1110 | 18,94 | 1110 | 37,88 |

| 1111 | 20,52 | 1111 | 41,04 |

Дифференциальный коэффициент усиления КИУ программируется битами GS[2:0] в регистре ASPM в соответствии с таблицей 7. С помощью бита IAD в регистре ASPM задается режим работы предусилителя: либо микромощный по току потребления, но с относительно большими шумами режим «прямого усиления», либо же режим со стабилизацией усилителя прерываниями, при котором низкочастотные шумы и ошибки по постоянному току существенно подавляются, но увеличивается потребление тока питания и уменьшается эффективное входное сопротивление (появляются небольшие входные токи). Режим со стабилизацией предусилителя прерываниями реализуется при IAD=1. Поскольку вышеуказанные положительные и отрицательные эффекты тем сильнее, чем выше частота прерываний, пользователю предоставляется возможность выбора (программирования) частоты стабилизации предусилителя прерыванием fИУ с помощью битов IAFDS[2:0] в регистре ASPCK2. При IAFDS[2:0]=000 или IAFDS[2:0]=001 предусилитель работает без прерываний. При инициализации микросхемы устанавливается IAFDS[2:0]=100, что задает частоту прерываний предусилителя fИУ=fАЦП/32 в зависимости от частоты выборок АЦП fАЦП. Еще четыре возможных варианта – fИУ=fАЦП/8, fИУ=fАЦП/16, fИУ=fАЦП/64 и fИУ=fАЦП/128. Поскольку частота fАЦП сама может выбираться в широких пределах, рекомендуется так программировать IAFDS[2:0], чтобы установить fИУ≈8 кГц.

Таблица 7. Программирование дифференциального коэффициента усиления КИУ битами GS[2:0]

| GS[2:0] | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

|---|---|---|---|---|---|---|---|---|

| КИУ | 1 | 4 | 8 | 16 | 32 | 64 | 128 | 256 |

Инструментальный усилитель можно отключить, сбросив бит PGIAEN в регистре ASPM. В этом случае сигналы IAINP и IAINN напрямую проходят на выходы IAOUTP и IAOUTN, соответственно.

В зависимости от временных и спектральных характеристик источника входных сигналов может быть полезно включение или отключение аналогового фильтра на входе АЦП. Эта возможность программируется битами RCS[1:0] в регистре ASPMUXS1. При установке, в том числе при инициализации микросхемы, RCS[1:0]=10 аналоговый фильтр включен. При задании RCS[1:0]=01 резисторы 640 кОм (см. рис. 7) шунтируются и сигналы IAOUTP и IAOUTN с выходов предусилителя без фильтрации поступают на входы буферов (повторителей) АЦП ADINP и ADINN, соответственно. Буферы обеспечивают высокое входное сопротивление для сигналов ADINP и ADINN, что актуально, например, при включенном аналоговом фильтре или при отключенном предусилителе. Если же высокое входное сопротивление не требуется, эти буферы можно отключить (шунтировать), установив бит BUFO=1 в регистре ASPM. При активированных буферах (BUFO=0) рабочий диапазон для сигналов ADINP и ADINN относительно общего (AVSS) составляет от 0,3 В до (AVDDR-0,9 В). Аналогично предусилителю, в буферах АЦП можно активировать режим стабилизации прерыванием. Его параметры программируются битами BUFFDS[1:0] в регистре ASPCK2. При включенном режиме стабилизации прерыванием уменьшаются НЧ шумы и ошибки по постоянному току, вносимые буферами. Однако это увеличивает потребление тока питания и добавляет входные токи. Поэтому, пользователю предоставляется возможность выбора (программирования) частоты стабилизации прерыванием (вышеуказанные положительные и отрицательные эффекты тем сильнее, чем выше частота прерываний). При BUFFDS[1:0]=00 буфер работает без прерываний. При инициализации SD6500 устанавливается BUFFDS[1:0]=01, что задает частоту прерываний буферов fБУФ=fАЦП/4. Еще два возможных варианта: fБУФ=fАЦП/8 и fБУФ=fАЦП/16. С выходов буферов сигналы INP и INN поступают на входы АЦП. Укрупненно схема АЦП показана на рисунке 9.

Рис. 9. Сигма-дельта АЦП в ИМС SD6500

На входы сигма-дельта модулятора поступают аналоговые сигналы INP и INN. К разности (INP – INN) добавляется программируемое постоянное смещение (для лучшего использования рабочего диапазона АЦП при обработке сигналов (INP – INN), имеющих диапазон изменения, существенно несимметричный относительно нуля). Сгенерированное таким образом входное напряжение АЦП сравнивается в модуляторе с опорным напряжением, формируя цифровой код DOUT. После его фильтрации цифровым фильтром получается 24-битный результат АЦ-преобразования (в трех регистрах ADCDH:ADCDM:ADCDL). Опорное напряжение АЦП, равно как и постоянное смещение по входу, формируется на основе разности напряжений VSP и VSN. Эти характеристики настраиваются битами VREFG[1:0] (в регистре ASPMUXS1) и DCSET[2:0] (в регистре DFM). Параметры работы цифрового фильтра АЦП (кратность оверсэмплинга) программируются битами OSR[2:0] (в регистре DFM). Частота выборок АЦП (частота модулятора) fАЦП задается битами в регистре ASPCK1. Напряжение VSP выбирается мультиплексором из вариантов AVDDR и ACM в соответствии с битами VREFS[1:0] (в регистре ASPMUXS1). Предусмотрено также мультиплексирование при задании VSN, но практически в SD6500 единственным вариантом выбора для него является аналоговый общий AVSS.

Рассмотрим работу АЦП чуть подробнее.

Входное (дифференциальное) напряжение АЦП UВХ АЦП=(INP – INN)×(3/4)+(VSP – VSN)×D,

где (INP – INN)=(IAINP – IAINN+VOS)×КИУ – дифференциальный сигнал с предусилителя;

(VSP – VSN)×D – постоянное смещение на входе АЦП;

D – масштабный коэффициент для постоянного смещения АЦП, задаваемый битами DCSET[2:0] в диапазоне [-3/4…3/4] с шагом 1/4.

Опорное напряжение АЦП UREF АЦП=(VSP – VSN)×G,

где G – масштабный коэффициент для опорного напряжения, задаваемый битами VREFG[1:0] из 4 вариантов: G=1/8; 1/4; 1/2; 1.

Для корректной работы АЦП UВХ АЦП должно находиться в пределах ± UREF АЦП. В противном случае произойдет переполнение. Результат АЦП представлен в дополнительном коде (старший бит в регистре ADCDH является знаковым: ADCDH[7]=0 для положительных напряжений UВХ АЦП и ADCDH[7]=1 – для отрицательных). При считывании результатов АЦП хост-контроллером первым должен читаться регистр ADCDH, затем – ADCDM и последним – ADCDL.

Частота выборок fАЦП программируется байтом ASPCK1[7:0], заданием соответствующего коэффициента деления для частоты ВЧ тактового генератора SD6500:

fАЦП=(fВЧ/8)/(256-ASPCK1[7:0]), но не более 512 кГц.

Кратность оверсэмплинга (отношение частоты выборок АЦП к частоте выдачи результатов цифровым фильтром АЦП) настраивается битами OSR[2:0] (в регистре DFM) в соответствии с таблицей 8.

Установкой бита TEN=1 в регистре ASPM инициируется измерение температуры чипа встроенным термодатчиком.

Таблица 8. Программирование оверсэмплинга цифрового фильтра АЦП битами OSR[2:0]

| OSR[2:0] | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

|---|---|---|---|---|---|---|---|---|

| Кратность оверсэмплинга | 128 | 256 | 512 | 1024 | 2048 | 4096 | 8192 | 16384 |

По результатам испытаний значительного количества экземпляров SD6500 получены фактические значения эффективного уровня шумов тракта ASP, приведенного ко входу малошумящего предусилителя, и соответствующих ему значений количества бит эффективного разрешения АЦП ENOB (выраженный в битах динамический диапазон АЦП выше эффективного уровня шума). Испытания проводились в 1024 точках для каждого экземпляра ИМС при различных, наиболее актуальных, комбинациях КИУ предусилителя, частоты АЦП fАЦП и кратности оверсэмплинга. Обобщенные результаты (при AVDDR=2,4 В; UREF АЦП=0,6 В; включенных буферах АЦП и цифровом фильтре SINC3) представлены в таблицах 9 и 10.

Таблица 9. Уровни шума, приведенные ко входу тракта ASP, и соответствующие им ENOB при fАЦП=128 кГц

| fАЦП=128 кГц | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| Кратность оверсэмплинга | 128 | 256 | 512 | 1024 | 2048 | 4096 | 8192 | 16384 | |

| КИУ=256 | ENOB | 14,9 | 15,4 | 16,0 | 16,5 | 16,9 | 17,4 | 17,9 | 18,4 |

| UВХ Ш ЭФФ, нВ | 298,9 | 210,5 | 144,1 | 102,5 | 73,7 | 52,0 | 36,9 | 27,5 | |

| КИУ=128 | ENOB | 15,8 | 16,3 | 16,8 | 17,3 | 17,8 | 18,4 | 18,9 | 19,3 |

| UВХ Ш ЭФФ, нВ | 322,2 | 219,8 | 153,9 | 109,5 | 76,3 | 53,6 | 38,5 | 28,7 | |

| КИУ=1 | ENOB | 16,9 | 17,9 | 18,4 | 19,0 | 19,5 | 20,0 | 20,4 | 20,9 |

| UВХ Ш ЭФФ, нВ | 19231 | 9838 | 6325 | 4560 | 3239 | 2306 | 1638 | 1222 | |

Таблица 10. Уровни шума, приведенные ко входу тракта ASP, и соответствующие им ENOB при fАЦП=512 кГц

| fАЦП=512 кГц | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| Кратность оверсэмплинга | 128 | 256 | 512 | 1024 | 2048 | 4096 | 8192 | 16384 | |

| КИУ=256 | ENOB | 14,2 | 14,7 | 15,2 | 15,7 | 16,2 | 16,7 | 17,2 | 17,7 |

| UВХ Ш ЭФФ, нВ | 490,9 | 346,8 | 247,5 | 176,1 | 123,3 | 86,7 | 63,7 | 45,3 | |

| КИУ=128 | ENOB | 15,1 | 15,6 | 16,0 | 16,6 | 17,1 | 17,5 | 18,0 | 18,5 |

| UВХ Ш ЭФФ, нВ | 539 | 380 | 278 | 191 | 135 | 97,9 | 70,9 | 50,7 | |

| КИУ=1 | ENOB | 16,8 | 17,8 | 18,3 | 18,8 | 19,3 | 19,8 | 20,3 | 20,8 |

| UВХ Ш ЭФФ, нВ | 20485 | 9958 | 6888 | 5002 | 3492 | 2539 | 1803 | 1253 | |

Если функционирование АЦП не требуется, для снижения потребляемого тока его можно отключить, сбросив бит ADCEN=0 в регистре ASPM. При этом автоматически отключается и питание буферов АЦП.

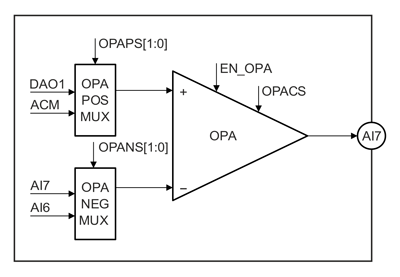

В составе SD6500 имеется многоцелевой операционный усилитель OPA (рисунок 10). Рабочие диапазоны напряжения на его входах (относительно AVSS) – от 0 до (AVDDR-0,7 В); на выходе, соответственно – от 0,2 В до (AVDDR-0,2 В). Управление усилителем производится битами в регистре OPASEL. Если работа усилителя не нужна, сбросив бит EN_OPA=0, его можно отключить, уменьшив потребление SD6500 (этот режим устанавливается при инициализации микросхемы). Манипулируя битом OPACS, можно инвертировать функционал входов усилителя: при OPACS=0 (устанавливается при инициализации микросхемы) неинвертирующий и инвертирующий входы соответствуют показанным на рисунке 10. При OPACS=1 входы инвертируются. При необходимости, периодически программно переключая бит OPACS, можно реализовать режим подавления напряжения смещения (ошибки) операционного усилителя OPA.

Рис. 10. Многоцелевой операционный усилитель OPA

Биты OPAPS[1:0] и OPANS[1:0] управляют мультиплексорами, переключающими входные сигналы на неинвертирующий и инвертирующий входы, соответственно. На неинвертирующий вход можно подать DAO1 или ACM, на инвертирующий – выбор между AI6 и AI7.

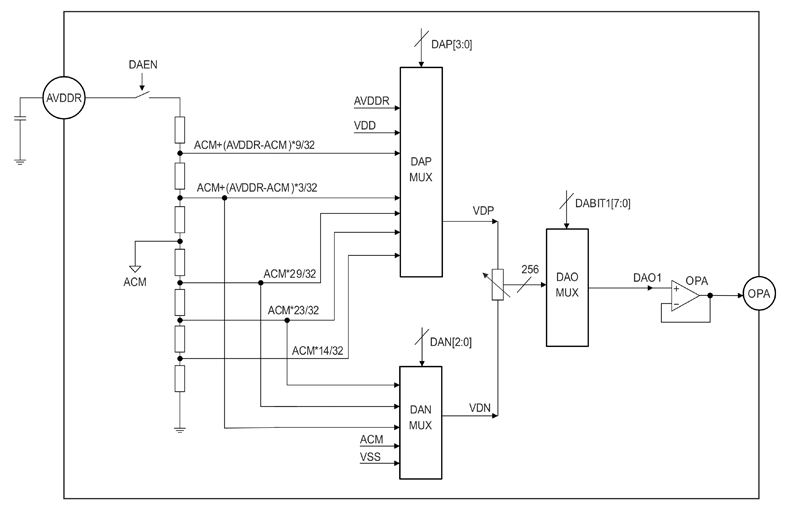

На рисунке 11 показана подсистема формирования требуемых аналоговых напряжений, называемая в документации SD6500 8-битным ЦАП. С ней ассоциированы конфигурационные регистры DASEL и DAO1. Основу ЦАП составляет 8-битный цифровой потенциометр, управляемый битами DABIT1[7:0] (в регистре DAO1). На крайние выводы потенциометра подаются предварительно сформированные аналоговые напряжения VDP и VDN. Со среднего вывода потенциометра (виртуального подвижного контакта) сигнал ЦАП DAO1 подается на повторитель (на основе операционного усилителя OPA, рассмотренного выше). С выхода повторителя сигнал ЦАП может быть мультиплексирован на внешний вывод ИМС.

Некоторые пояснения по принципу действия цифрового потенциометра:

DAO1=VDN+(VDP – VDN)/256×DABIT1[7:0], где DABIT1 принимает значения от 0 до 255 (при инициализации микросхемы устанавливается 0). Напряжения VDP и VDN формируются двумя мультиплексорами DAPMUX и DANMUX, управляемыми, соответственно, битами DAP[3:0] и DAN[2:0] (в регистре DASEL).

Рис. 11. 8-битный ЦАП

Напряжение VDP выбирается из семи рабочих вариантов (остальные девять – зарезервированные или некорректные). Напряжение VDN выбирается из пяти рабочих вариантов (остальные три – зарезервированные или некорректные). В качестве вариантов для выбора могут использоваться как фиксированные напряжения (VDD, AVDDR, ACM, AVSS), так и сформированные на цепочке резисторов. Сопротивления резисторов в этой цепочке имеют определенные соотношения между собой. Цепочка в двух или трех точках подключена к фиксированным потенциалам: общий (AVSS), ACM, а также – через переключатель – AVDDR. Переключатель управляется битом DAEN в регистре DASEL. Таким образом, напряжение VDN может изменяться от нуля до (AVDDR×3+ACM×29)/32. Соответственно, напряжение VDP может изменяться от ACM×14/32 до VDD. В результате, на выходе ЦАП DAO1 можно получать как напряжения, весьма близкие к границам внешнего питания (общий и VDD), так и устанавливать с весьма высоким разрешением (эффективно 11…12 бит) напряжения, близкие к ACM или к половинному значению AVDDR.

SD6500 может быть с успехом использована в разнообразных измерительных и управляющих системах, преимущественно ориентированных на микропотребление (автономное и батарейное питание), малые габариты, низкую стоимость при невысоких требованиях по быстродействию. В качестве целевых областей применения указываются весы (или датчики давления), глюкометры и пирометры.

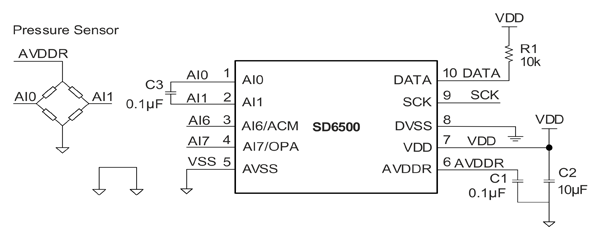

На рисунке 12 приведена схема весов, использующая мост тензорезисторов (хост-контроллер, подключенный по цепям DVSS, VDD, SCK и DATA, условно не показан).

Рис. 12. Схема высокоточных весов на основе ИМС SD6500

Достаточно большая нагрузочная способность по выходу AVDDR (вывод 6 микросхемы SD6500) позволяет запитать тензомост весов или датчика давления стабилизированным напряжением при обычных сопротивлениях тензорезисторов ≥500 Ом. С измерительной диагонали моста сигналы подаются на входы AI0 и AI1. При синфазном напряжении, близком к половине напряжения питания, требуется с высокой точностью измерять малую разницу напряжений AI0 и AI1: SD6500 отлично подходит для этого. Для уменьшения влияния внешних помех на точность измерений, при невысоких требованиях по быстродействию, полезно шунтировать измерительную диагональ моста конденсатором С3.

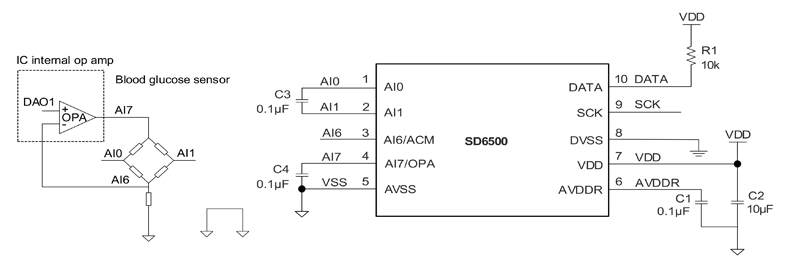

На рисунке 13 приведена схема измерителя концентрации глюкозы в крови. Датчиком является специализированный, чувствительный к содержанию глюкозы резистивный мост. Для его корректной работы требуется стабилизировать ток, протекающий по резисторам моста. С этой целью мост питается с выхода операционного усилителя (вывод 4 ИМС «OPA»), имеющегося в составе SD6500, охваченного отрицательной обратной связью по току (вывод 3 ИМС «AI6»), через дополнительный резистор – датчик тока. Желаемое значение тока можно задать с помощью сигнала ЦАП DAO1. Выход операционного усилителя шунтирован конденсатором С4=100 нФ. В остальном схема совпадает с показанной на рисунке 12.

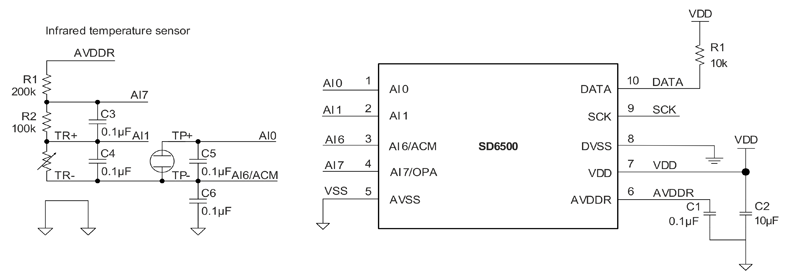

На рисунке 14 приведена схема инфракрасного термометра. Датчик запитан от AVDDR и ACM. Измеряются аналоговые сигналы AI0, AI1, AI7. При соответствующей модификации датчика по сравнению с рисунками 12 и 13, сами принципы построения измерительной системы на основе SD6500 остаются неизменными.

Рис. 13. Схема измерителя концентрации глюкозы в крови на основе ИМС SD6500

Рис. 14. Схема инфракрасного термометра на основе ИМС SD6500

Компания SDIC разрабатывает и производит широкий ассортимент аналого-цифровых измерительных систем-на-кристалле. ИМС SD6500 представляет одну из наиболее простых, микропотребляющих, малогабаритных и недорогих систем класса «analog-front-end». Она позволяет строить разнообразные измерительные и управляющие приборы с высокими характеристиками. ИМС SD6500 доступна для приобретения в КОМПЭЛ по весьма привлекательной цене.

Наши информационные каналы